MIT6.S081笔记:lecture 4

MIT6.S081笔记:lecture 4 Page Tables

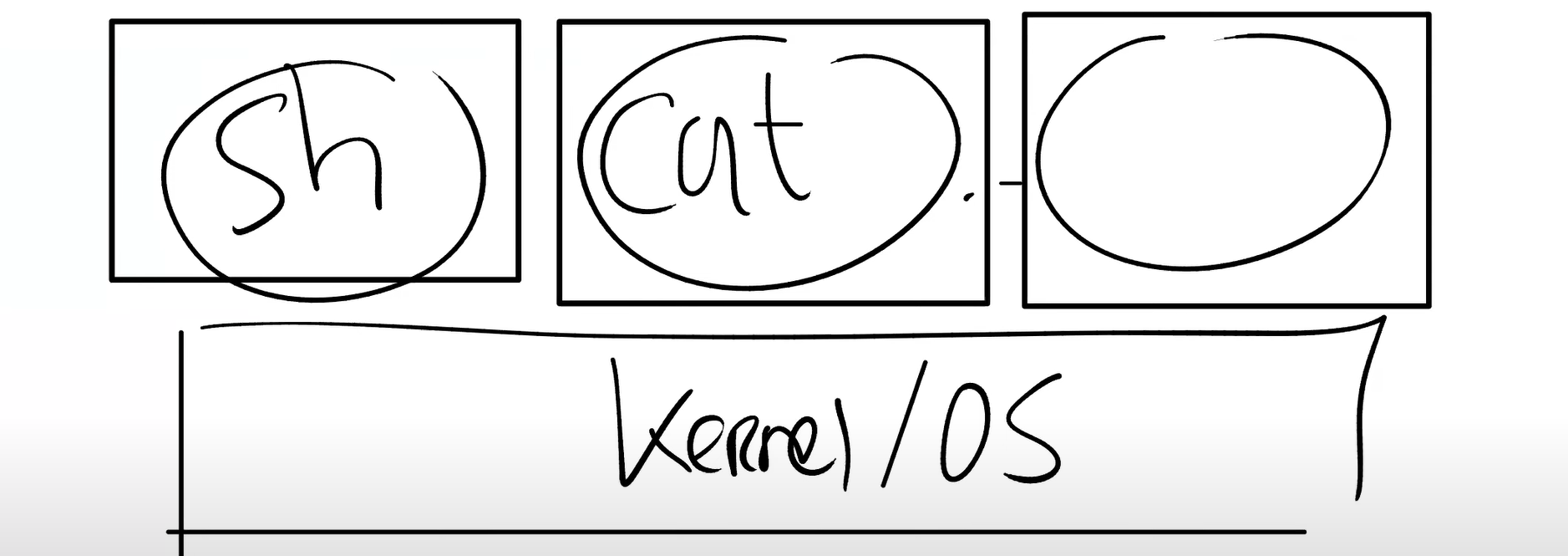

Isolation

- why use virtual memory?

- make bad code doesn’t affect the os

- want sth really seperates these memories from different programs

How to give isolation?

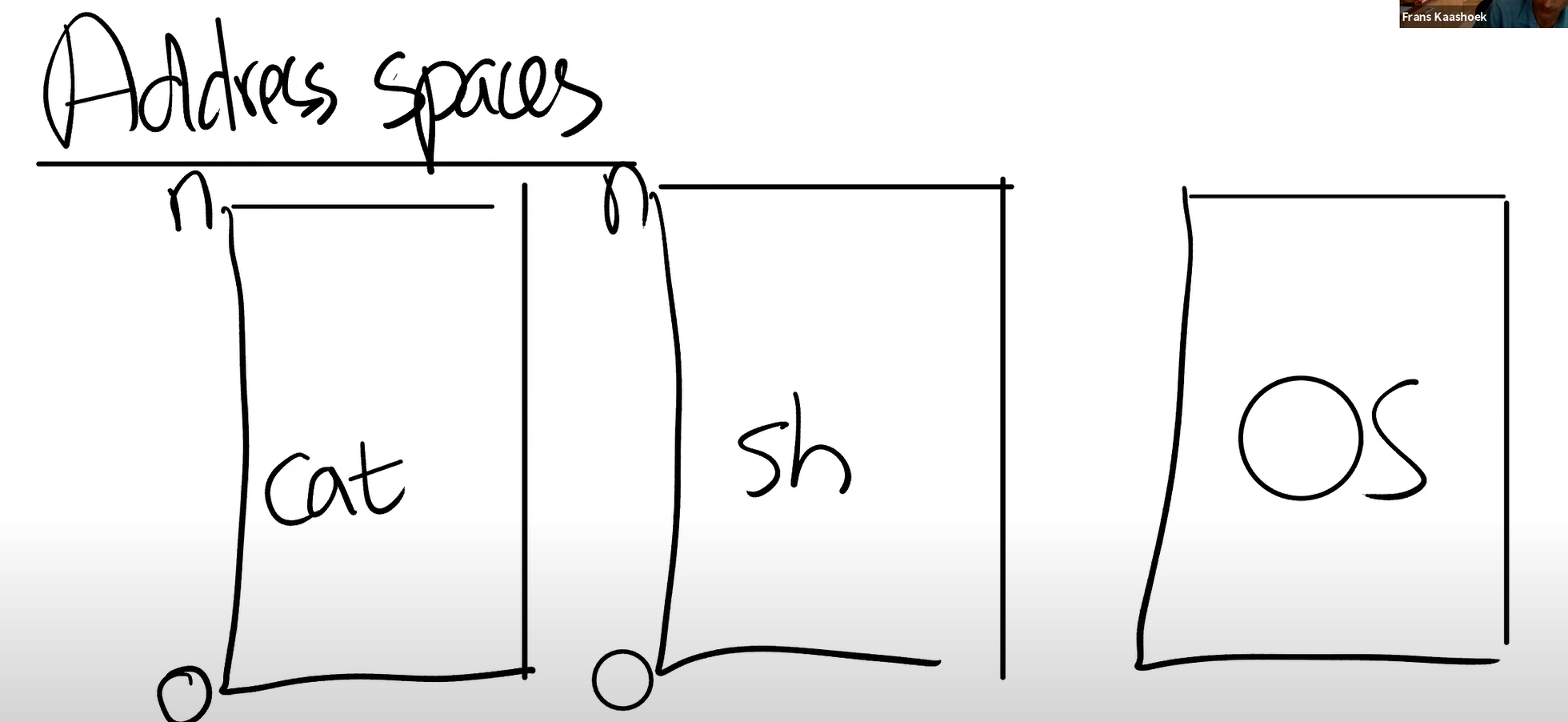

Address Spaces

- give applications including the kernel its own address space

How to multiplex all these different address spaces on a single physical memory?

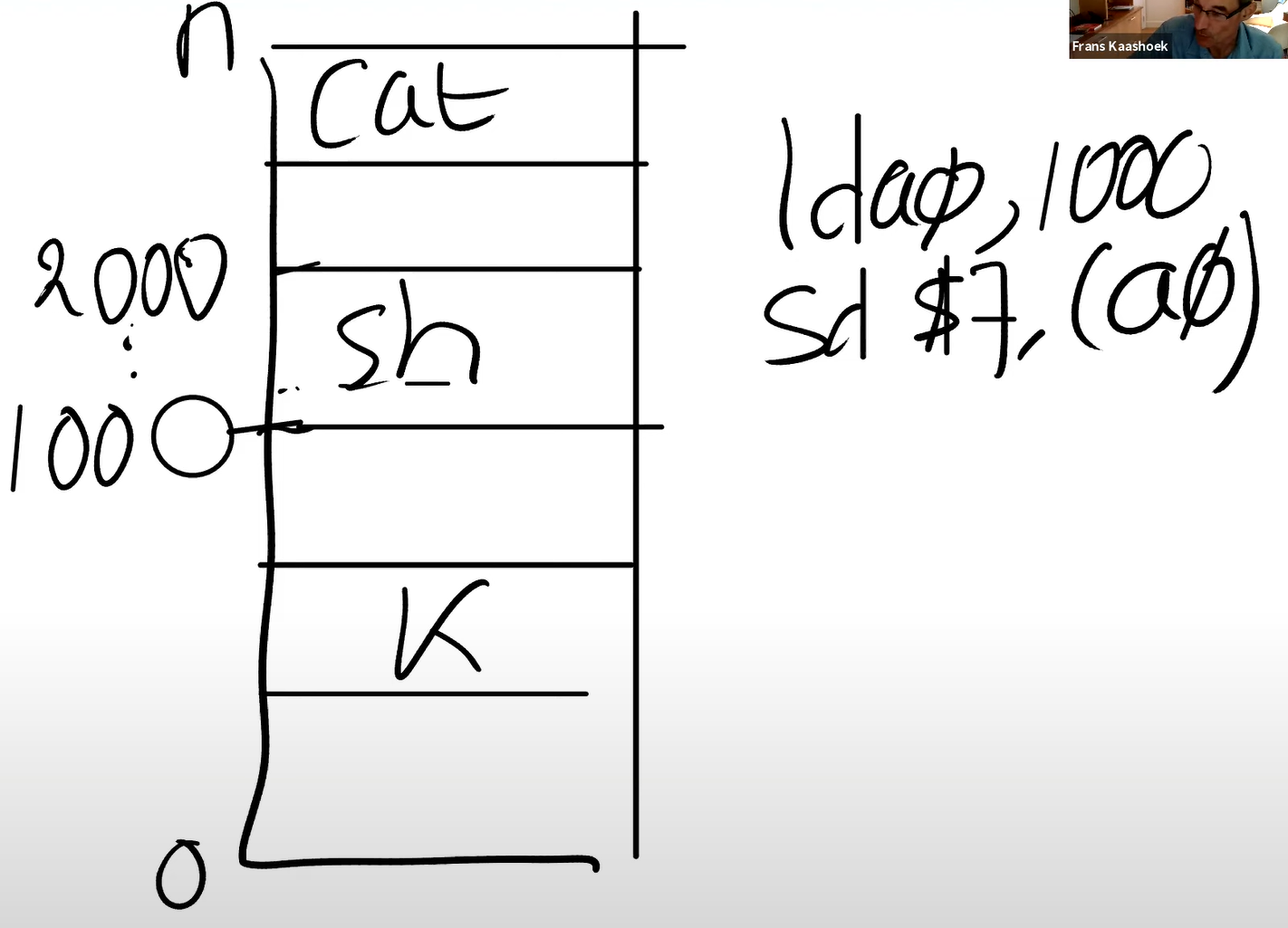

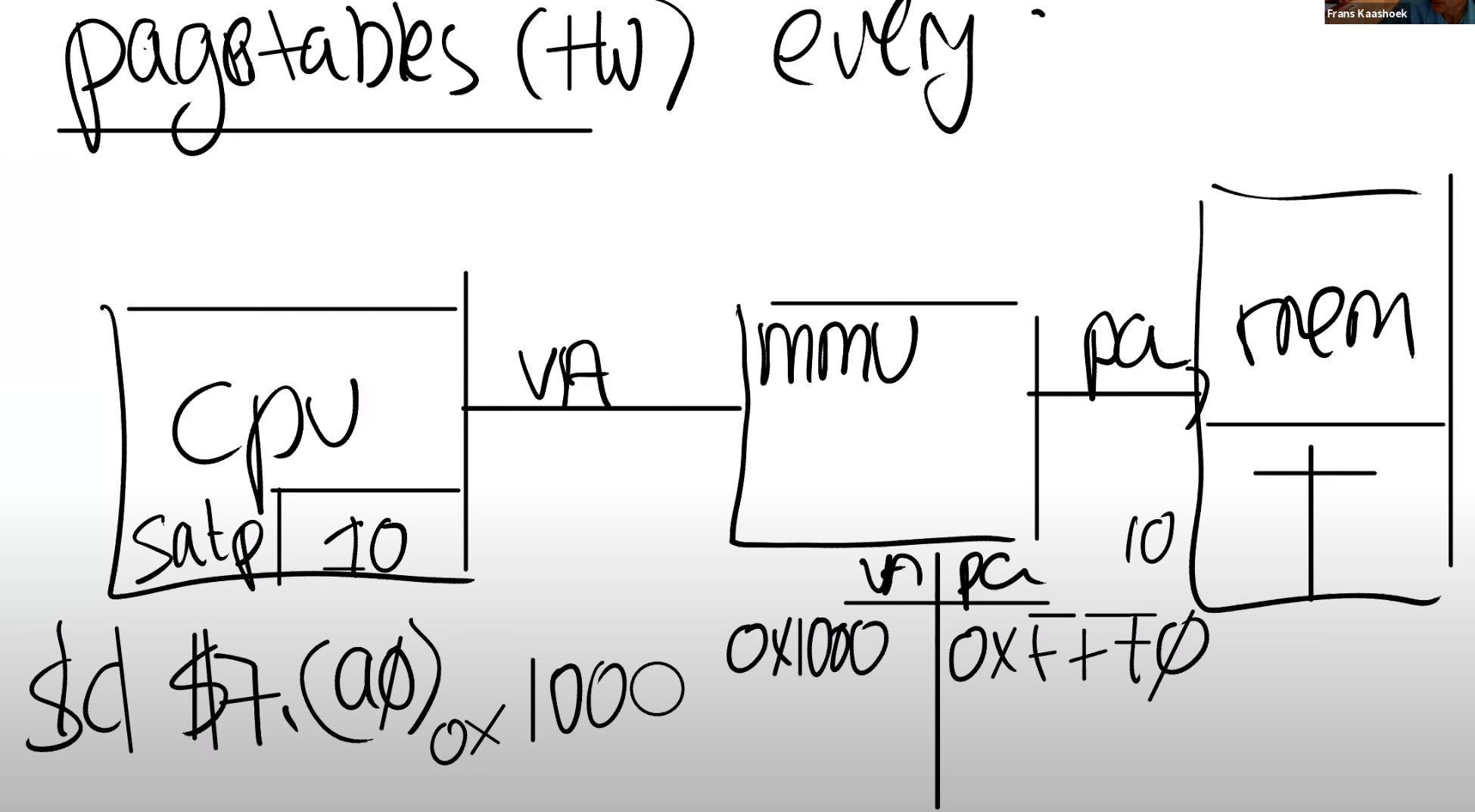

PAGE TABLES (HW: memory management unit)

Blueprint

- every app has its own map which basically defines its address space

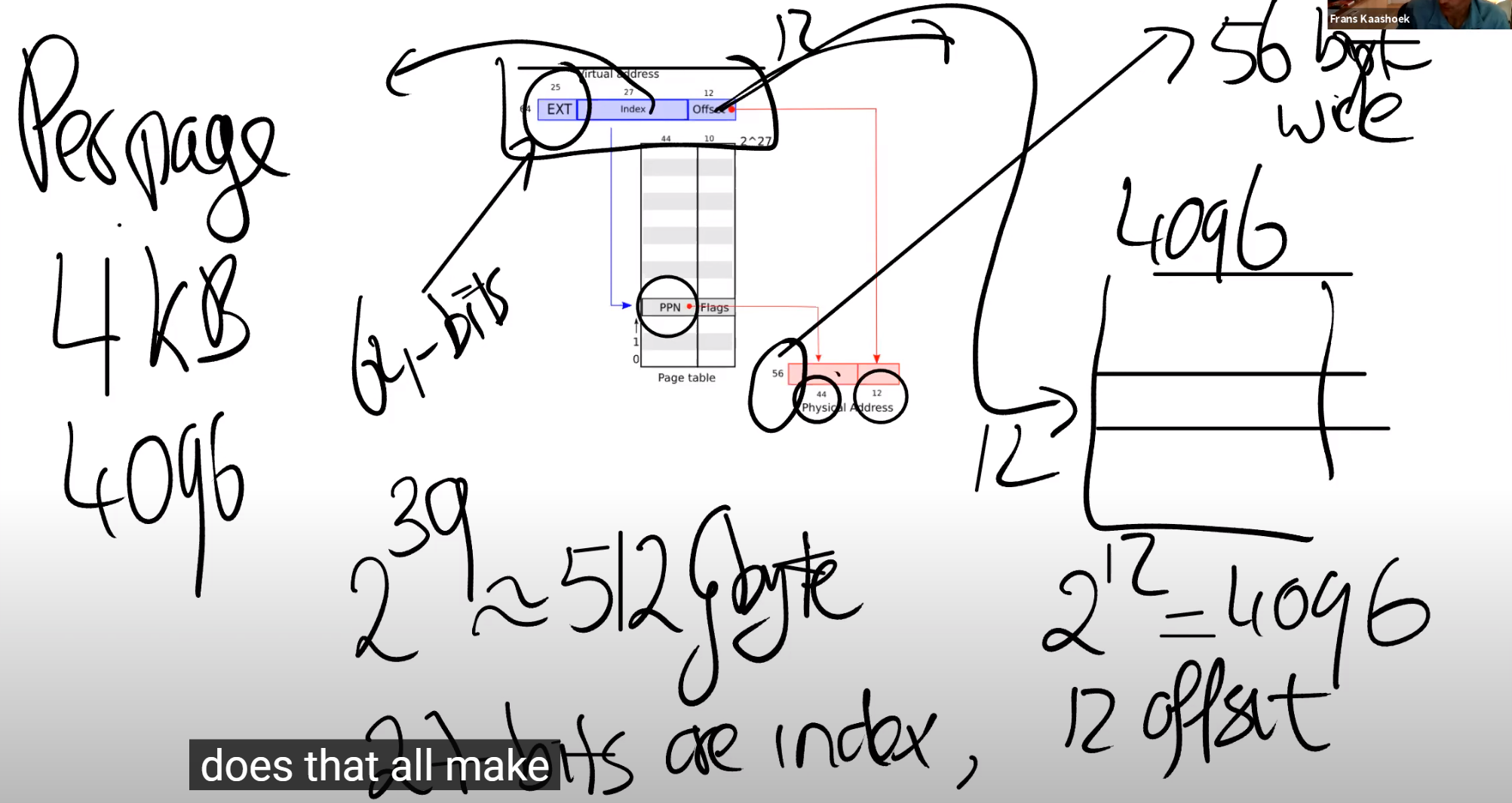

PAGE TABLE

- not per address, per page! each page is 4kB

- in xv6, virtual memory is less than physical memory space

- and it’s inefficient to store all entries(2^27)

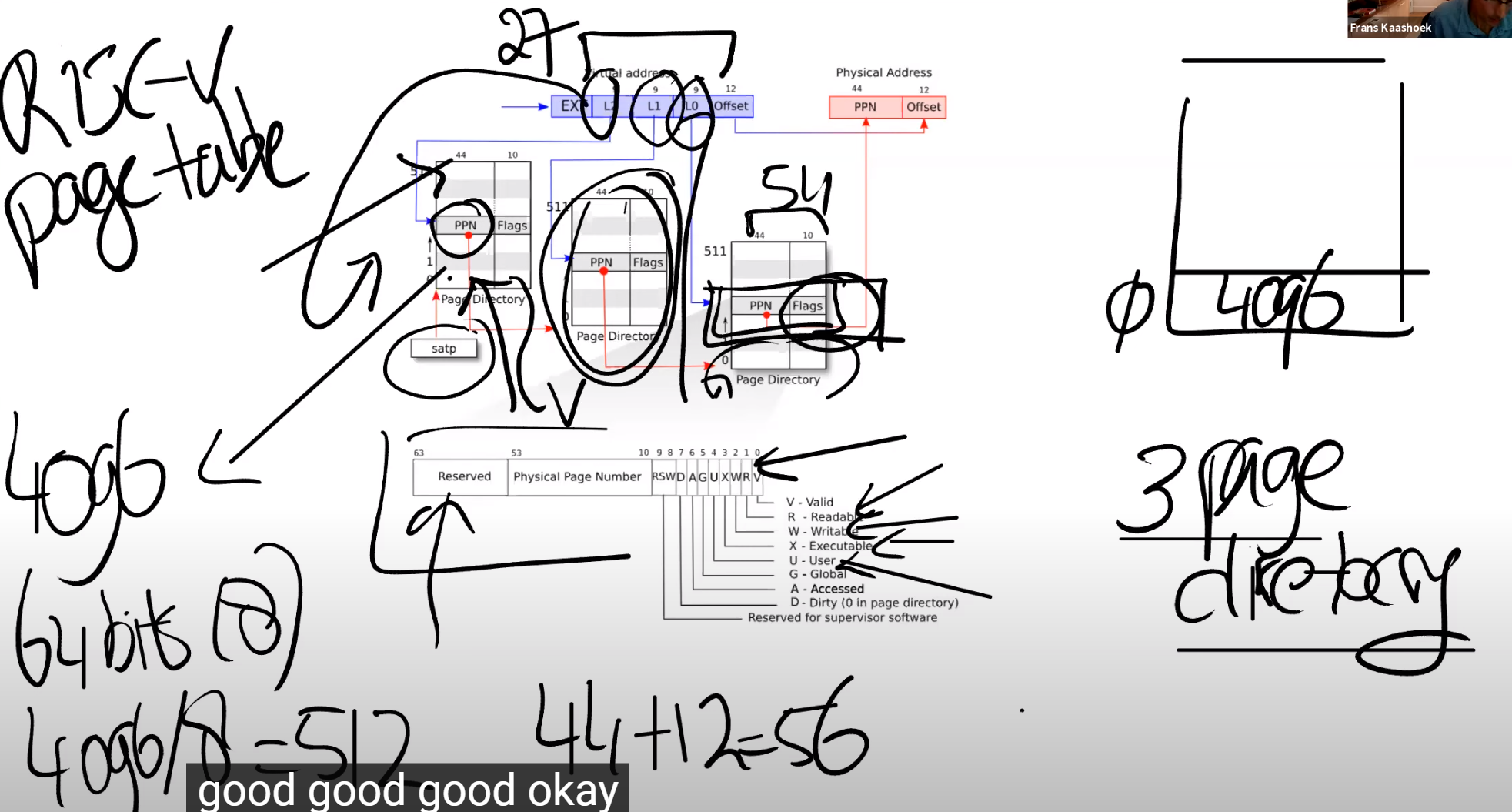

RISC-V PAGE TABLE

- Use cache(TLB) to avoid 3 times of memory translations

- When switching page table, also need to flush the TLB

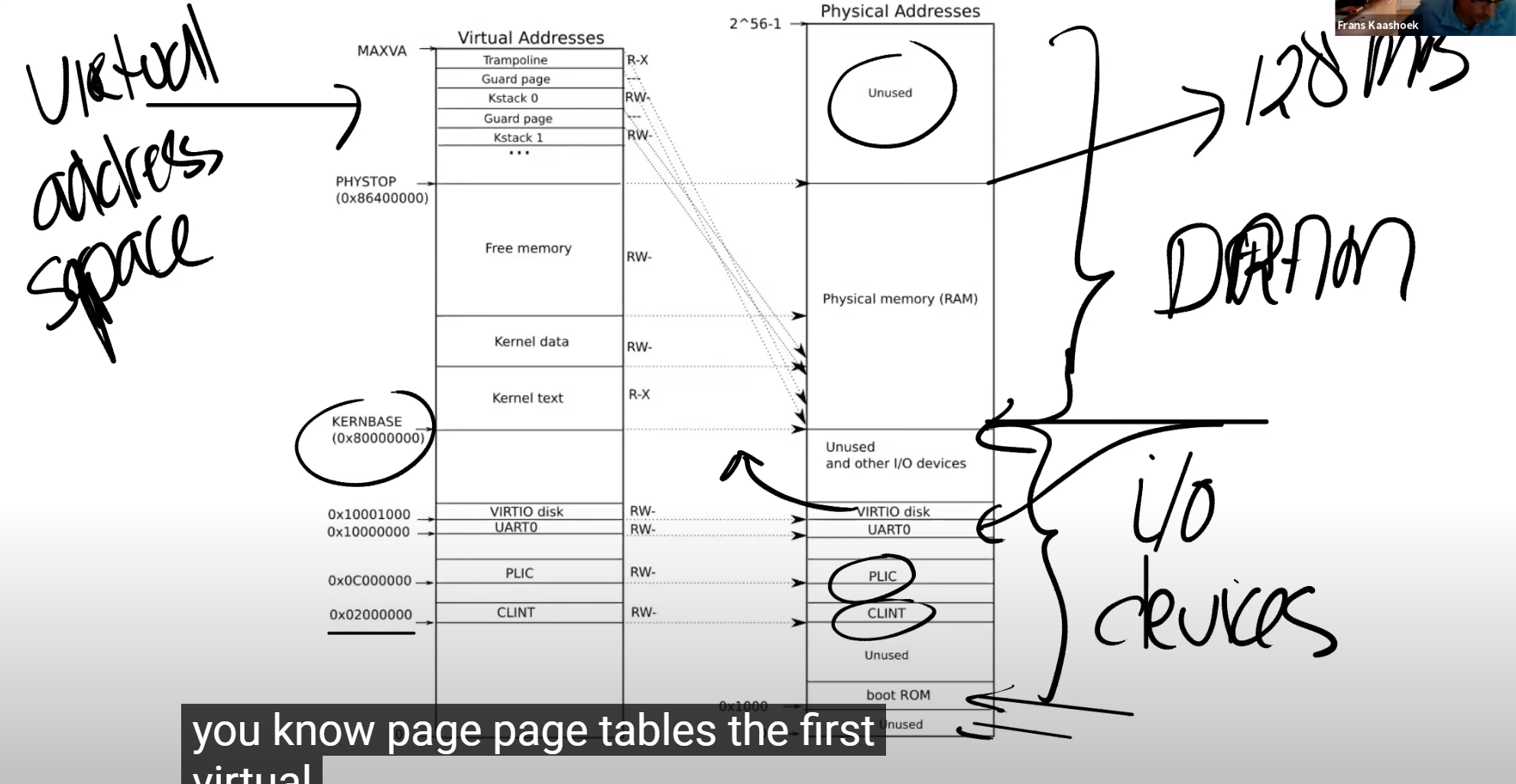

Kernel memory address space layout

- every process has a corresponding kernel stack

- Post title:MIT6.S081笔记:lecture 4

- Post author:sixwalter

- Create time:2023-08-05 11:14:26

- Post link:https://coelien.github.io/2023/08/05/course-learning/MIT6.S081/lec4/

- Copyright Notice:All articles in this blog are licensed under BY-NC-SA unless stating additionally.

Comments